組み込みエンジニアの皆さん、日々の業務お疲れ様です!IoTデバイスから産業機器まで、私たちの生活を支える様々な製品に組み込まれたFPGA。その高性能さゆえに、どうしてもコストがネックになること、ありますよね。「もっとコストを抑えられたら、新しいプロジェクトにもっと予算を割けるのに…」そう思っている方も少なくないのではないでしょうか?今回は、そんな悩みを抱えるあなたに、信号処理FPGAのコスト削減に繋がる秘策を伝授します。これまで多くのエンジニアが試行錯誤してきたノウハウを凝縮し、明日から使える具体的な方法をまとめました。ぜひ最後まで読んで、あなたのプロジェクトに役立ててください。

この記事で得られること

この記事では、信号処理FPGAのコスト削減に関する以下の知識や情報が得られます。

- FPGAのコスト構造を理解し、削減の余地を見つける方法

- 具体的なコスト削減戦略(設計、開発、運用)

- 最適なFPGA選定のためのポイント

- 最新トレンドと将来展望

この記事を読むことで、あなたはFPGAのコストを最適化し、より多くのプロジェクトに挑戦できるようになるでしょう。また、最新の技術動向を把握することで、競争力を高めることができるはずです。

FPGAコストの構造を徹底解剖!ボトルネックはどこにある?

FPGAのコスト削減に取り組む前に、まずはそのコスト構造をしっかりと理解することが重要です。FPGAのコストは、大きく分けて「初期費用」と「運用費用」の2つに分類できます。初期費用には、FPGAデバイス自体の購入費用、開発ツール(コンパイラ、デバッガなど)のライセンス費用、そして設計・開発にかかる人件費などが含まれます。一方、運用費用には、FPGAの消費電力に関わる電気代、冷却にかかる費用、そして故障時の交換費用などが含まれます。

特に初期費用の中でも、FPGAデバイス自体の価格は大きな割合を占めます。高性能なFPGAほど高価になる傾向があり、プロジェクトの予算を圧迫する要因となります。また、開発ツールのライセンス費用も、複数人で開発を行う場合はそれなりの金額になります。人件費も、設計の複雑さや開発期間によって大きく変動するため、注意が必要です。

運用費用については、特に消費電力が重要です。FPGAは処理能力が高い反面、消費電力も大きくなりがちです。そのため、冷却にかかる費用も無視できません。また、FPGAは故障のリスクもゼロではありません。故障時の交換費用も考慮しておく必要があります。

これらのコスト要素を把握した上で、どこに削減の余地があるのかを見極めることが、コスト削減の第一歩です。例えば、初期費用を抑えるためには、より安価なFPGAを選定したり、オープンソースの開発ツールを活用したりするなどの方法が考えられます。運用費用を抑えるためには、低消費電力な設計を心がけたり、効率的な冷却システムを導入したりするなどの対策が必要です。

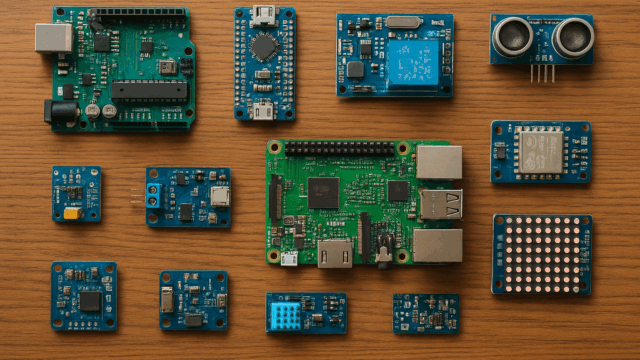

提案画像: FPGAが搭載された基板と、その基板を設計しているエンジニアの様子を捉えた写真。エンジニアは真剣な表情でモニターを見つめている。

提案画像: FPGAが搭載された基板と、その基板を設計しているエンジニアの様子を捉えた写真。エンジニアは真剣な表情でモニターを見つめている。

設計段階から始めるコスト削減術:性能を維持しつつ無駄を省く

FPGAのコスト削減は、設計段階から意識することが非常に重要です。性能を維持しつつ無駄を省くためには、様々なテクニックを駆使する必要があります。まず、回路規模の削減が挙げられます。回路規模が小さくなれば、使用するFPGAのサイズを小さくすることができ、デバイスコストを抑えることができます。回路規模を削減するためには、アルゴリズムの見直しや、回路の共有化などが有効です。例えば、複数の処理で共通の演算処理を行う場合、その部分を共通化することで回路規模を削減できます。

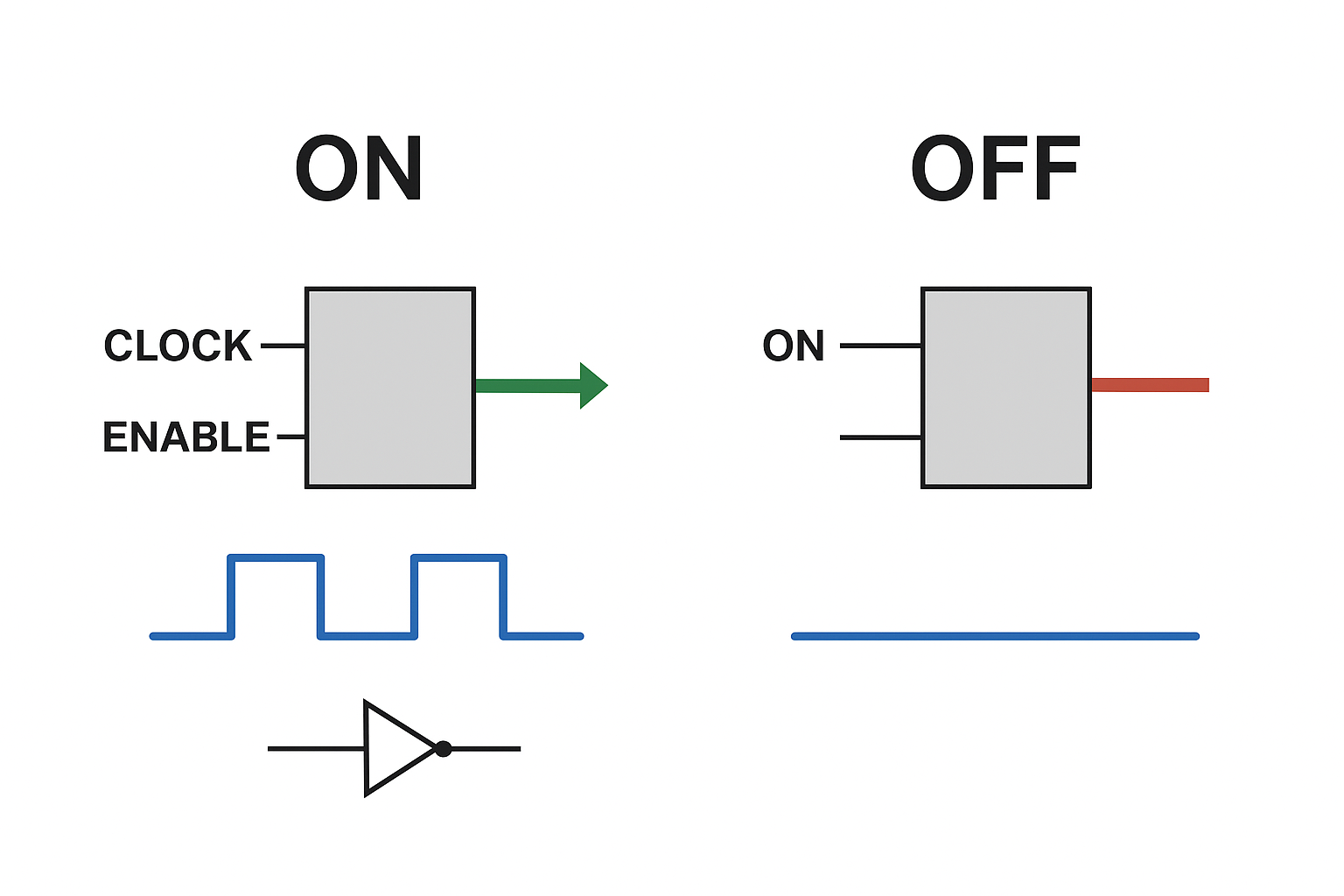

次に、クロック周波数の最適化も重要です。クロック周波数が高すぎると、消費電力が増加し、冷却コストも増加します。必要な性能を満たす範囲で、できるだけ低いクロック周波数で動作するように設計することで、消費電力を抑えることができます。また、FPGAには、クロックゲーティングやパワーゲーティングなどの省電力機能が搭載されている場合があります。これらの機能を積極的に活用することで、さらに消費電力を削減することができます。

さらに、IPコアの活用も有効な手段です。IPコアとは、特定の機能を実現するための回路ブロックのことで、FPGAベンダーやサードパーティから提供されています。IPコアを活用することで、自分で回路を設計する手間を省き、開発期間を短縮することができます。また、IPコアは最適化されている場合が多く、自分で設計するよりも高性能かつ低消費電力な回路を実現できる可能性があります。

例えば、高速フーリエ変換(FFT)処理を行う場合、FPGAベンダーから提供されているFFT IPコアを活用することで、自分でFFT回路を設計するよりも、より効率的な回路を短期間で実現できます。ただし、IPコアのライセンス費用が発生する場合があるため、コストと性能のバランスを考慮して選択する必要があります。

また、制約ドリブン設計を導入することも有効です。制約ドリブン設計とは、性能、消費電力、コストなどの制約条件を設計ツールに入力し、その制約条件を満たすように自動的に回路を生成する設計手法です。制約ドリブン設計を活用することで、最適な回路を効率的に設計することができます。

FPGA選定の落とし穴:隠れたコストを見抜く目を養う

FPGAの選定は、コスト削減において非常に重要なステップです。しかし、FPGAのデータシートに記載されているスペックだけを見て選んでしまうと、後々になって隠れたコストに気づくことがあります。例えば、FPGAの価格だけでなく、開発ツールのライセンス費用や、消費電力、パッケージ、入手性なども考慮する必要があります。

まず、開発ツールのライセンス費用は、FPGAベンダーによって大きく異なります。無償の開発ツールが提供されている場合もあれば、高額なライセンス費用が必要な場合もあります。開発ツールは、設計、シミュレーション、デバッグなど、FPGAの開発に必要なすべての機能を提供している必要があります。また、使いやすさも重要です。使いにくい開発ツールを使用すると、開発期間が長くなり、人件費が増加する可能性があります。

次に、消費電力は、運用コストに直接影響します。消費電力が大きいFPGAを使用すると、電気代や冷却コストが増加します。特に、24時間365日稼働するようなシステムでは、消費電力の差が大きなコスト差となって現れます。FPGAのデータシートに記載されている消費電力だけでなく、実際の動作条件での消費電力を評価することが重要です。

また、パッケージも重要な要素です。パッケージの種類によって、基板設計の難易度や、実装コストが異なります。例えば、BGAパッケージは、QFPパッケージよりも小型化できますが、基板設計が難しく、実装コストも高くなります。プロジェクトの要件に合わせて、最適なパッケージを選択する必要があります。

さらに、FPGAの入手性も考慮する必要があります。特定のFPGAが、常に安定して入手できるとは限りません。供給が不安定なFPGAを選んでしまうと、プロジェクトの遅延や、代替品の選定が必要になる可能性があります。FPGAベンダーの供給状況を確認し、長期的に安定して入手できるFPGAを選ぶことが重要です。

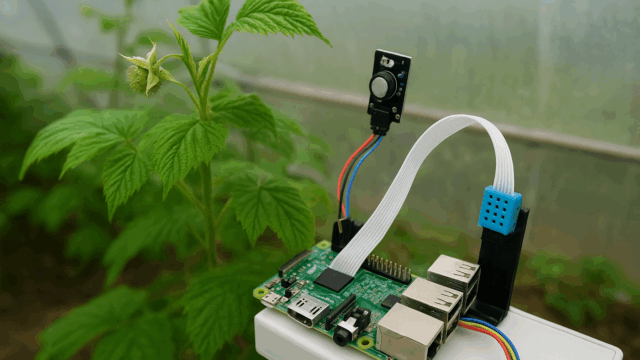

提案画像: 様々な種類のFPGAチップが並んでいる様子を捉えた写真。それぞれのチップには型番が記載されている。

提案画像: 様々な種類のFPGAチップが並んでいる様子を捉えた写真。それぞれのチップには型番が記載されている。

最新トレンドと将来展望:コスト削減の新たな可能性

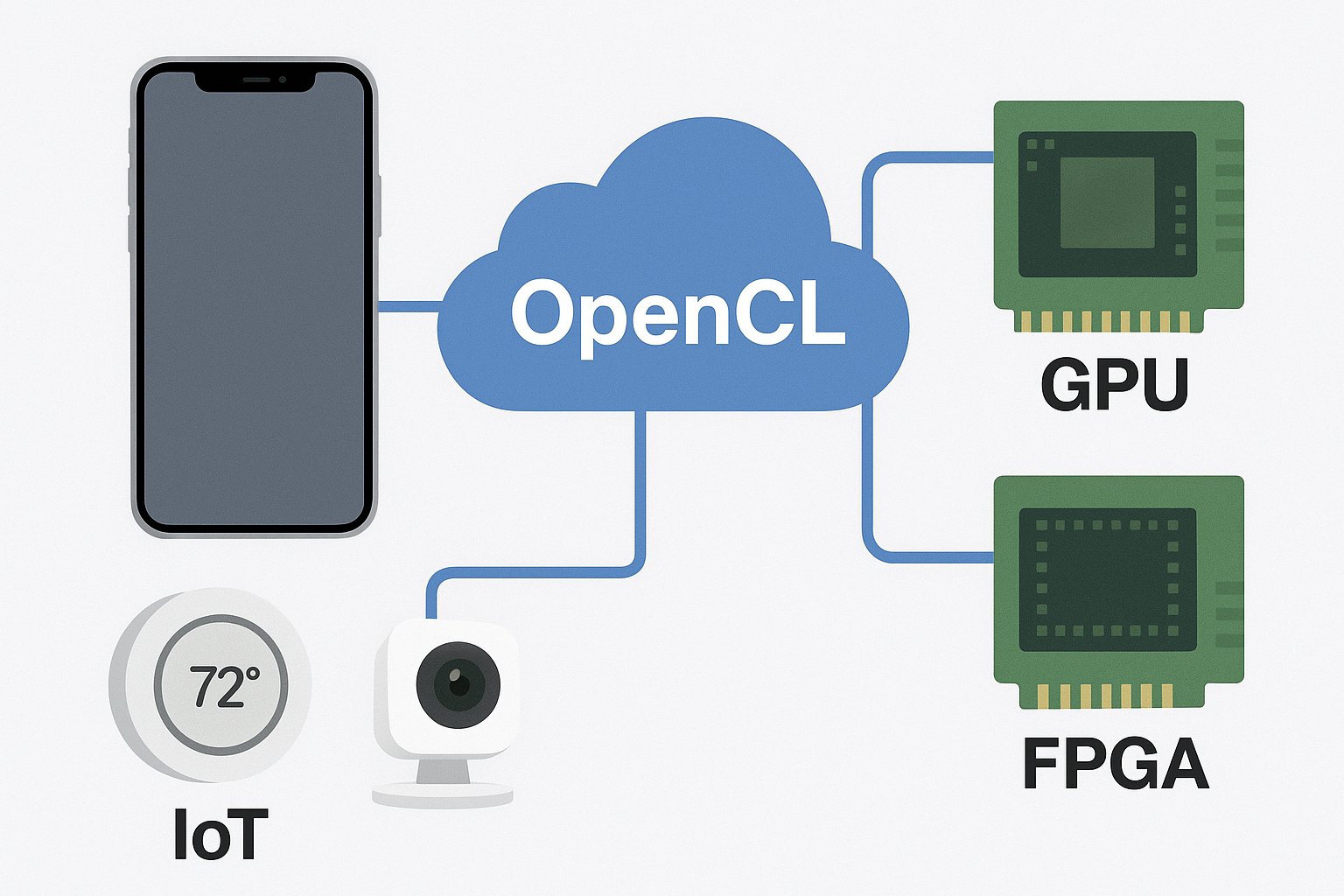

FPGAのコスト削減は、常に進化し続けています。近年では、新しい技術やトレンドが登場し、コスト削減の新たな可能性を広げています。例えば、クラウドFPGAは、必要な時に必要なだけFPGAリソースを利用できるため、初期費用を大幅に削減することができます。クラウドFPGAは、FPGAをクラウド上で利用できるサービスで、オンプレミスのFPGAと同様に、自由に回路を設計・実装することができます。クラウドFPGAを利用することで、高価なFPGAデバイスを購入する必要がなくなり、初期費用を大幅に削減することができます。また、必要な時に必要なだけリソースを利用できるため、無駄なコストを削減することができます。

また、高位合成(HLS)ツールも注目されています。高位合成ツールは、C/C++などの高級言語で記述されたプログラムを、FPGAのハードウェア記述言語(HDL)に自動変換するツールです。高位合成ツールを使用することで、HDLの知識がなくてもFPGAの設計が可能になり、開発期間を短縮することができます。また、高位合成ツールは、回路の最適化も自動で行ってくれるため、高性能かつ低消費電力な回路を簡単に実現することができます。

さらに、チップレット技術も今後のトレンドとして注目されています。チップレット技術とは、複数の小さなチップを組み合わせて、一つの大きなチップとして動作させる技術です。チップレット技術を活用することで、異なるプロセス技術で製造されたチップを組み合わせたり、必要な機能だけを搭載したチップを組み合わせたりすることが可能になり、コストを最適化することができます。例えば、高性能なロジック回路は、最先端のプロセス技術で製造し、低速なインターフェース回路は、旧世代のプロセス技術で製造することで、全体のコストを削減することができます。

これらの最新トレンドを常に把握し、積極的に取り入れることで、FPGAのコスト削減の可能性をさらに広げることができます。また、FPGAベンダーやサードパーティからの情報も積極的に収集し、最新の技術動向を把握することも重要です。例えば、FPGAベンダーが開催するセミナーや、展示会などに参加することで、最新の技術情報を入手することができます。

提案画像: クラウド上にFPGAリソースが展開されているイメージ図。複数のサーバーがネットワークで接続され、FPGAのアイコンが表示されている。

提案画像: クラウド上にFPGAリソースが展開されているイメージ図。複数のサーバーがネットワークで接続され、FPGAのアイコンが表示されている。

まとめ:コスト削減は継続的な努力で、競争力UPへ!

今回は、信号処理FPGAのコスト削減について、様々な角度から解説しました。FPGAのコスト構造を理解し、設計段階からコストを意識し、最適なFPGAを選定し、最新トレンドを取り入れることで、コスト削減を実現することができます。しかし、コスト削減は、一度行ったら終わりではありません。継続的な努力が必要です。常に新しい技術やトレンドを把握し、改善を続けることで、FPGAのコストを最適化し、競争力を高めることができます。

FPGAのコスト削減は、単にコストを抑えるだけでなく、新しいプロジェクトに挑戦するための資金を確保したり、製品の価格競争力を高めたりすることにも繋がります。また、環境負荷を低減することにも貢献できます。FPGAのコスト削減は、企業の成長と社会貢献の両立に繋がる重要な取り組みです。

この記事が、あなたのFPGAコスト削減の一助となれば幸いです。ぜひ、この記事で得た知識や情報を活用して、あなたのプロジェクトを成功に導いてください。そして、より多くの人々に、FPGAの可能性を広げていきましょう。

さあ、一歩踏み出そう!

この記事を読んで、FPGAのコスト削減に興味を持った方は、ぜひ今日から行動を開始しましょう。まずは、あなたのプロジェクトで使用しているFPGAのコスト構造を分析し、削減の余地を見つけることから始めてみてください。そして、この記事で紹介したテクニックやトレンドを参考に、具体的なコスト削減策を検討してみてください。

もし、FPGAの選定や設計についてお困りの場合は、FPGAベンダーやサードパーティの専門家に相談することも有効です。専門家のアドバイスを受けることで、より効率的にコスト削減を進めることができます。また、FPGAに関するコミュニティに参加することもおすすめです。コミュニティでは、他のエンジニアと情報交換をしたり、相談に乗ってもらったりすることができます。一人で悩まずに、積極的に情報収集や交流を行い、FPGAの知識やスキルを高めていきましょう。

さあ、あなたもFPGAのコスト削減に挑戦し、より魅力的な製品を開発しましょう!