組み込みエンジニアの皆さん、日々の開発お疲れ様です!IoTデバイスから産業機器まで、あらゆるシーンで省電力化が求められる昨今、クロックゲーティングはまさに必須の技術ですよね。でも、いざ実装しようとすると、どこから手を付ければいいのか、本当に効果があるのか、悩ましい点も多いのではないでしょうか?この記事では、そんな皆さんの疑問を解消し、クロックゲーティングを最大限に活用するための最適解を、わかりやすく解説していきます。

この記事を通じて、クロックゲーティングの基本的な概念から、具体的な設計・実装方法、そして効果測定まで、一連の流れを理解していただくことを目指します。さらに、陥りやすい落とし穴や、より高度な省電力化手法についても触れていきます。クロックゲーティングをマスターし、あなたの開発するデバイスのバッテリー寿命を劇的に向上させましょう!

クロックゲーティングとは?その基本と重要性

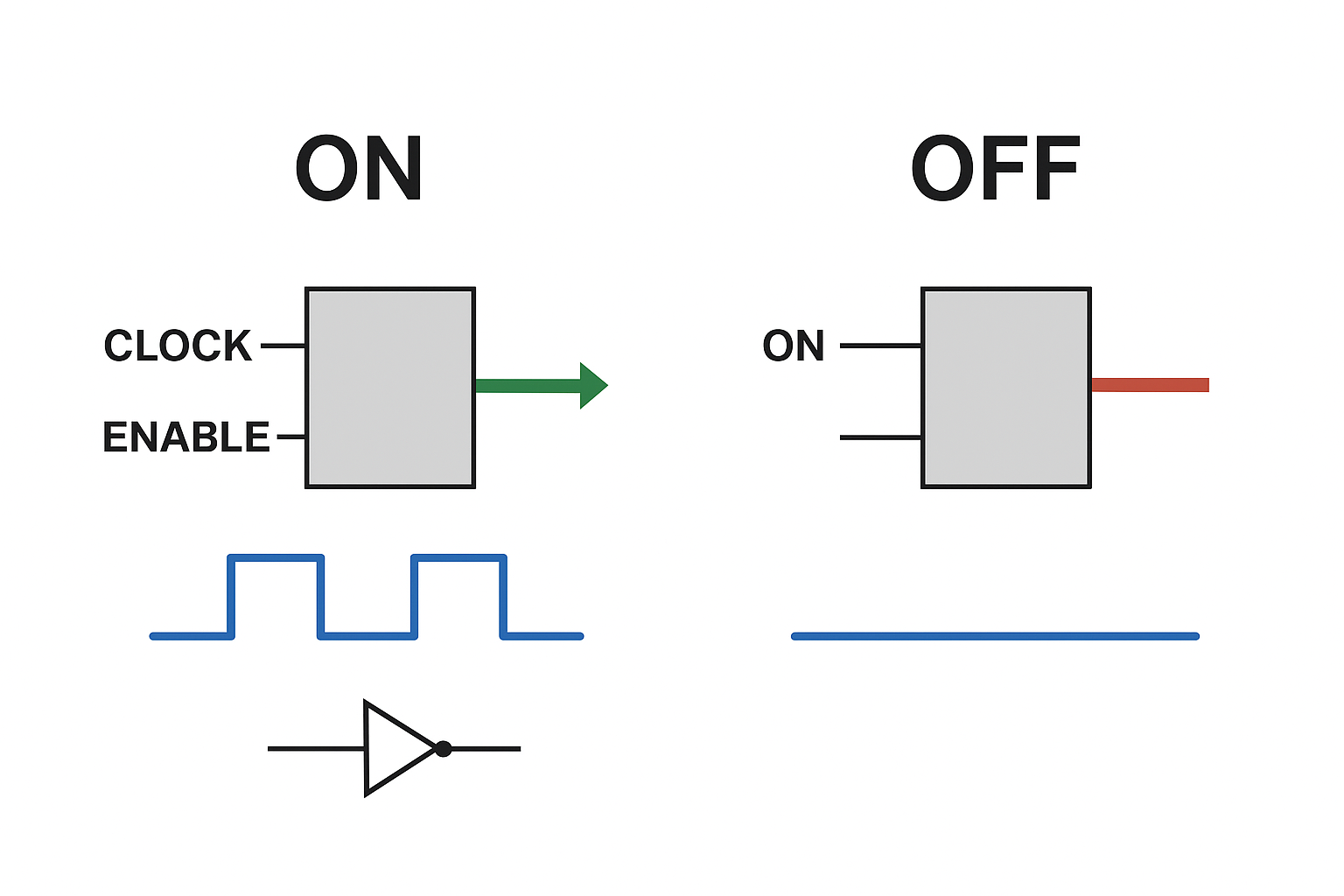

クロックゲーティングとは、簡単に言うと「必要な時だけクロック信号を供給し、不要な時は止める」という省電力化技術です。デジタル回路は、クロック信号に合わせて動作するため、クロックが供給されている限り、たとえ何も処理していなくても電力を消費します。クロックゲーティングは、この無駄な電力消費を抑えるために、回路の動作状況に応じてクロック信号をON/OFFすることで、大幅な省電力化を実現します。

組み込み機器における省電力化は、バッテリー駆動時間の延長、発熱の抑制、そして環境負荷の低減に直結します。特にIoTデバイスのように、常に動作している必要がある機器では、わずかな電力消費の削減が、大きな差となって現れます。クロックゲーティングは、ハードウェアレベルでの省電力化アプローチとして、非常に有効な手段の一つと言えるでしょう。

クロックゲーティングには、大きく分けて「粗粒度クロックゲーティング」と「細粒度クロックゲーティング」の2種類があります。粗粒度クロックゲーティングは、機能ブロック単位でクロックをON/OFFする方式で、比較的実装が容易ですが、省電力効果は限定的です。一方、細粒度クロックゲーティングは、より細かい回路単位でクロックを制御するため、高い省電力効果が期待できますが、設計・実装の難易度が高くなります。どちらの方式を選択するかは、システムの要件や設計リソースに応じて検討する必要があります。

提案画像: クロックゲーティングのON/OFF状態を示す図解。クロック信号が供給されている状態と、停止している状態が明確にわかるように表現されている。

提案画像: クロックゲーティングのON/OFF状態を示す図解。クロック信号が供給されている状態と、停止している状態が明確にわかるように表現されている。

近年では、EDAツール(電子設計自動化ツール)の進化により、細粒度クロックゲーティングの設計・実装が以前よりも容易になっています。これらのツールを活用することで、より高度な省電力化設計を効率的に行うことが可能です。

クロックゲーティングの実装:設計から検証まで

クロックゲーティングを実際に実装する際には、いくつかの重要なステップがあります。まずは、クロックゲーティングを適用する対象回路を特定することから始めます。電力消費の大きい回路や、動作頻度の低い回路が、クロックゲーティングの適用対象として適しています。回路の動作特性を十分に理解し、クロックゲーティングによって性能に悪影響が出ないことを確認する必要があります。

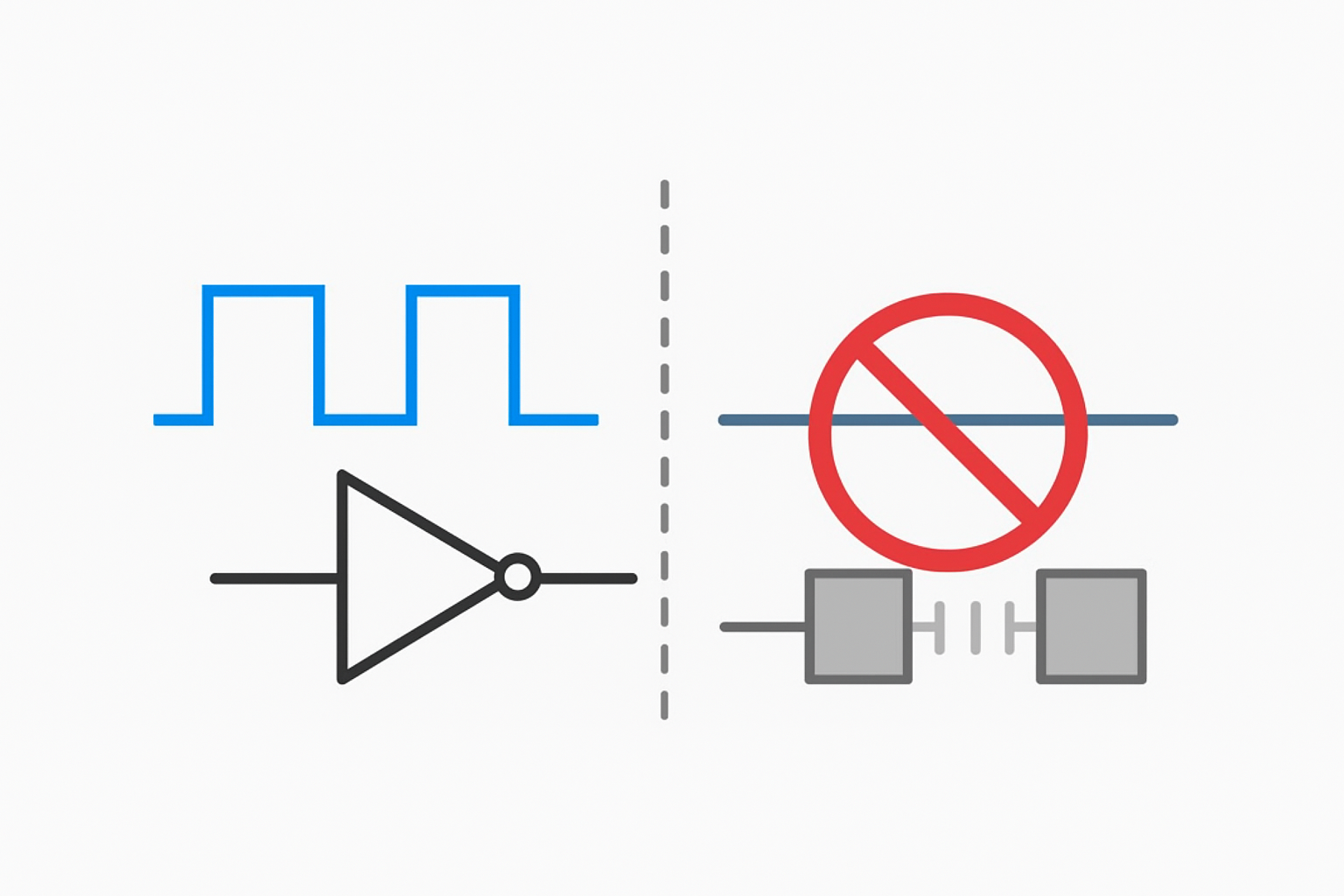

次に、クロックゲーティング回路の設計を行います。クロックゲーティング回路は、ANDゲートやラッチ回路などを用いて実現できます。クロック信号をON/OFFするための制御信号は、回路の動作状態に応じて生成する必要があります。制御信号の生成には、ステートマシンやコンパレータなどが用いられます。制御信号のタイミング設計は、クロックゲーティング回路の性能に大きく影響するため、慎重に行う必要があります。

クロックゲーティング回路の設計が終わったら、シミュレーションによる検証を行います。シミュレーションでは、回路の動作状態を網羅的に検証し、クロックゲーティング回路が正しく動作することを確認します。タイミングマージンやセットアップ/ホールドタイムなどのタイミング制約も検証する必要があります。シミュレーションの結果、問題が見つかった場合は、回路の設計を見直す必要があります。

提案画像: クロックゲーティング回路の具体的な回路図。ANDゲートやラッチ回路がどのように接続され、クロック信号を制御しているのかがわかるように表現されている。

提案画像: クロックゲーティング回路の具体的な回路図。ANDゲートやラッチ回路がどのように接続され、クロック信号を制御しているのかがわかるように表現されている。

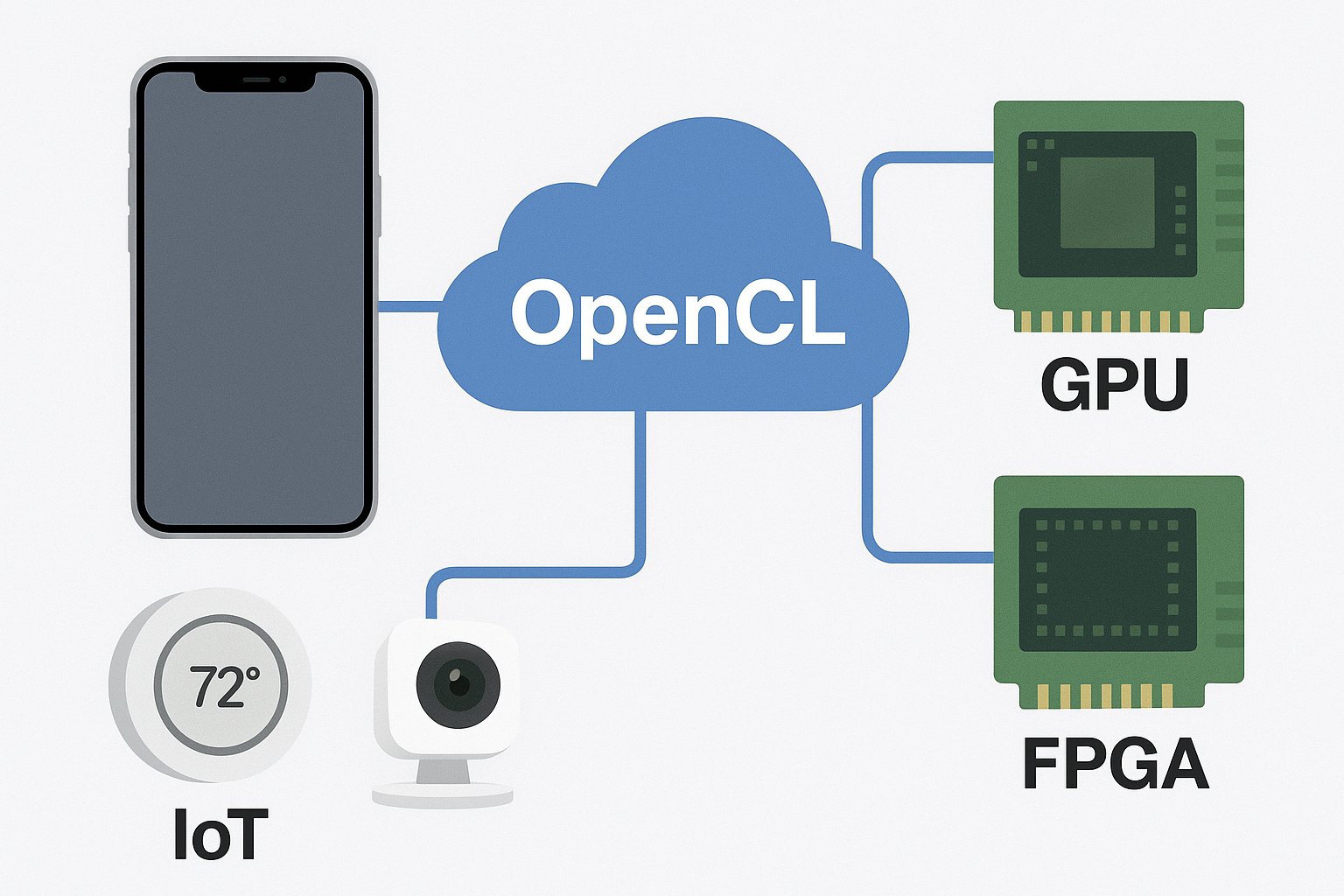

クロックゲーティング回路の実装には、FPGA(Field Programmable Gate Array)やASIC(Application Specific Integrated Circuit)などのハードウェア記述言語(HDL)を用いるのが一般的です。HDLには、VerilogやVHDLなどがあります。HDLを用いてクロックゲーティング回路を記述し、論理合成ツールを用いて回路を実装します。論理合成ツールは、HDLで記述された回路を、実際のハードウェアにマッピングします。

クロックゲーティングの効果測定と高度な省電力化

クロックゲーティングを実装したら、実際にどの程度省電力化できたのかを評価する必要があります。効果測定には、消費電力測定器やシミュレーションツールなどを用います。消費電力測定器を用いる場合は、クロックゲーティングを適用する前後の消費電力を測定し、その差を比較します。シミュレーションツールを用いる場合は、回路の動作状態をシミュレーションし、消費電力を推定します。

クロックゲーティングの効果は、回路の動作状態やクロック周波数、そしてクロックゲーティング回路の設計によって大きく異なります。効果測定の結果、期待したほどの省電力効果が得られなかった場合は、クロックゲーティング回路の設計を見直す必要があります。より細粒度のクロックゲーティングを適用したり、制御信号のタイミングを最適化したりすることで、省電力効果を向上させることができます。

クロックゲーティング以外にも、様々な省電力化技術があります。例えば、電圧スケーリングは、動作電圧を下げることで消費電力を削減する技術です。周波数スケーリングは、動作周波数を下げることで消費電力を削減する技術です。これらの技術をクロックゲーティングと組み合わせることで、さらなる省電力化を実現できます。

近年では、AI(人工知能)を活用した省電力化技術も注目されています。AIは、回路の動作状態を学習し、最適なクロックゲーティング制御を行うことができます。AIを活用することで、より高度な省電力化を実現できる可能性があります。

提案画像: 消費電力測定器を用いて、実際にクロックゲーティングの効果を測定している様子。測定結果のグラフなどが表示されている。

提案画像: 消費電力測定器を用いて、実際にクロックゲーティングの効果を測定している様子。測定結果のグラフなどが表示されている。

省電力化は、組み込みエンジニアにとって永遠の課題です。クロックゲーティングをマスターし、様々な省電力化技術を組み合わせることで、より高性能で省電力なデバイスを開発していきましょう。

まとめ:クロックゲーティングで省電力化を極める

この記事では、クロックゲーティングの基本から実装、効果測定、そして高度な省電力化技術まで、幅広く解説してきました。クロックゲーティングは、組み込み機器の省電力化に非常に有効な技術であり、IoT時代を生き抜くためには必須の知識と言えるでしょう。

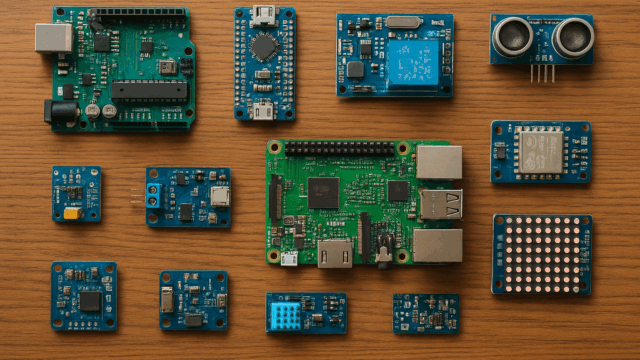

クロックゲーティングをマスターするためには、実際に回路を設計・実装し、効果を検証することが重要です。EDAツールや開発キットを活用し、積極的にクロックゲーティングに挑戦してみましょう。最初はうまくいかないこともあるかもしれませんが、試行錯誤を繰り返すことで、必ずやクロックゲーティングのコツを掴むことができるはずです。

省電力化は、技術者としての腕の見せ所でもあります。クロックゲーティングを駆使し、あなたの開発するデバイスのバッテリー寿命を劇的に向上させ、世界をより持続可能なものにしていきましょう!

次のステップへ:更なる知識を深めよう

この記事を読んで、クロックゲーティングに興味を持っていただけたでしょうか?もしそうなら、ぜひ当サイトの他の記事もチェックしてみてください。リアルタイムOS、エッジコンピューティング、ドライバー開発など、組み込みソフトウェアに関する様々な情報を提供しています。あなたの知識とスキルを向上させるためのヒントが、きっと見つかるはずです。

また、組み込みソフトウェアに関する質問や相談があれば、お気軽にお問い合わせください。経験豊富なエンジニアが、あなたの疑問にお答えします。一緒に組み込みソフトの世界を探求し、未来を切り拓いていきましょう!